Der D-FET befindet sich in der 0-Gate-Vorspannung, wenn der Kanal vorhanden ist und der FET leiten kann. Wenn kein Kanal vorhanden ist, befindet sich der E-FET in der 0-Gate-Vorspannung und kann den FET nicht leiten. Diese beiden Arten von FETs haben ihre eigenen Eigenschaften und Verwendungszwecke. Im Allgemeinen sind verbesserte FETs in Hochgeschwindigkeitsschaltungen mit geringem Stromverbrauch sehr wertvoll. und dieses Gerät funktioniert, es ist die Polarität der Gate-Vorspannung voBehälter und Abfluss Spannung des gleichen, es ist bequemer im Schaltungsdesign.

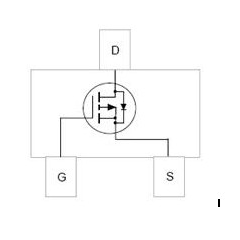

Das sogenannte „Enhanced“ bedeutet: Wenn die Röhre VGS = 0 ist und die korrekte VGS in einem abgeschnittenen Zustand ist, werden die meisten Ladungsträger vom Gate angezogen, wodurch die Ladungsträger in der Region „verstärkt“ werden und ein leitender Kanal gebildet wird. Der n-Kanal-verstärkte MOSFET ist im Grunde eine links-rechts-symmetrische Topologie, bei der der P-Typ-Halbleiter eine SiO2-Filmisolationsschicht erzeugt. Es erzeugt eine isolierende Schicht aus einem SiO2-Film auf dem P-Typ-Halbleiter und diffundiert dann zwei hochdotierte N-Typ-Bereiche durchFotolithographie, und führt Elektroden aus dem N-Typ-Bereich, eine für den Drain D und eine für die Source S. Eine Schicht aus Aluminiummetall wird auf die Isolierschicht zwischen der Source und dem Drain als Gate G plattiert. Wenn VGS = 0 V , es gibt eine ganze Reihe von Dioden mit Back-to-Back-Dioden zwischen Drain und Source und die Spannung zwischen D und S bildet keinen Strom zwischen D und S. Der Strom zwischen D und S wird nicht durch die angelegte Spannung gebildet .

Wenn die Gate-Spannung hinzugefügt wird und 0 < VGS < VGS(th), werden durch das kapazitive elektrische Feld, das zwischen dem Gate und dem Substrat gebildet wird, die Polyonlöcher im P-Typ-Halbleiter nahe der Unterseite des Gates nach unten abgestoßen, und es entsteht eine dünne Verarmungsschicht aus negativen Ionen; Gleichzeitig wird es die darin enthaltenen Oligogone anziehen, um sich zur Oberflächenschicht zu bewegen. Die Anzahl ist jedoch begrenzt und reicht nicht aus, um einen leitenden Kanal zu bilden, der Drain und Source verbindet, sodass sie immer noch nicht ausreicht, um einen Drain-Strom-ID zu bilden. weiteren Anstieg VGS, wenn VGS > VGS (th) (VGS (th) wird als Einschaltspannung bezeichnet), da zu diesem Zeitpunkt die Gate-Spannung relativ stark war und sich in der P-Typ-Halbleiteroberflächenschicht nahe der Unterseite des Gates mehr ansammelt Elektronen können einen Graben bilden, den Abfluss und die Kommunikationsquelle. Wenn zu diesem Zeitpunkt die Drain-Source-Spannung hinzugefügt wird, kann der Drain-Strom ID gebildet werden. Elektronen im leitenden Kanal bilden sich unterhalb des Gates, da die Polarität des Trägerlochs mit dem P-Typ-Halbleiter entgegengesetzt ist und daher als Anti-Typ-Schicht bezeichnet wird. Während VGS weiter zunimmt, wird die ID weiter zunehmen. ID = 0 bei VGS = 0 V und der Drain-Strom tritt erst auf, wenn VGS > VGS(th), daher wird dieser MOSFET-Typ als Anreicherungs-MOSFET bezeichnet.

Die Steuerbeziehung von VGS zum Drainstrom kann durch die Kurve iD = f(VGS(th))|VDS=const, die als Übertragungskennlinie bezeichnet wird, und die Größe der Steigung der Übertragungskennlinie, gm, beschrieben werden. spiegelt die Steuerung des Drain-Stroms durch die Gate-Source-Spannung wider. Die Größe von gm beträgt mA/V, daher wird gm auch Transkonduktanz genannt.